TSMC’s Compounding Machine (And What Could Interrupt It)

The reinvestment math, the learning curve, and the geopolitics.

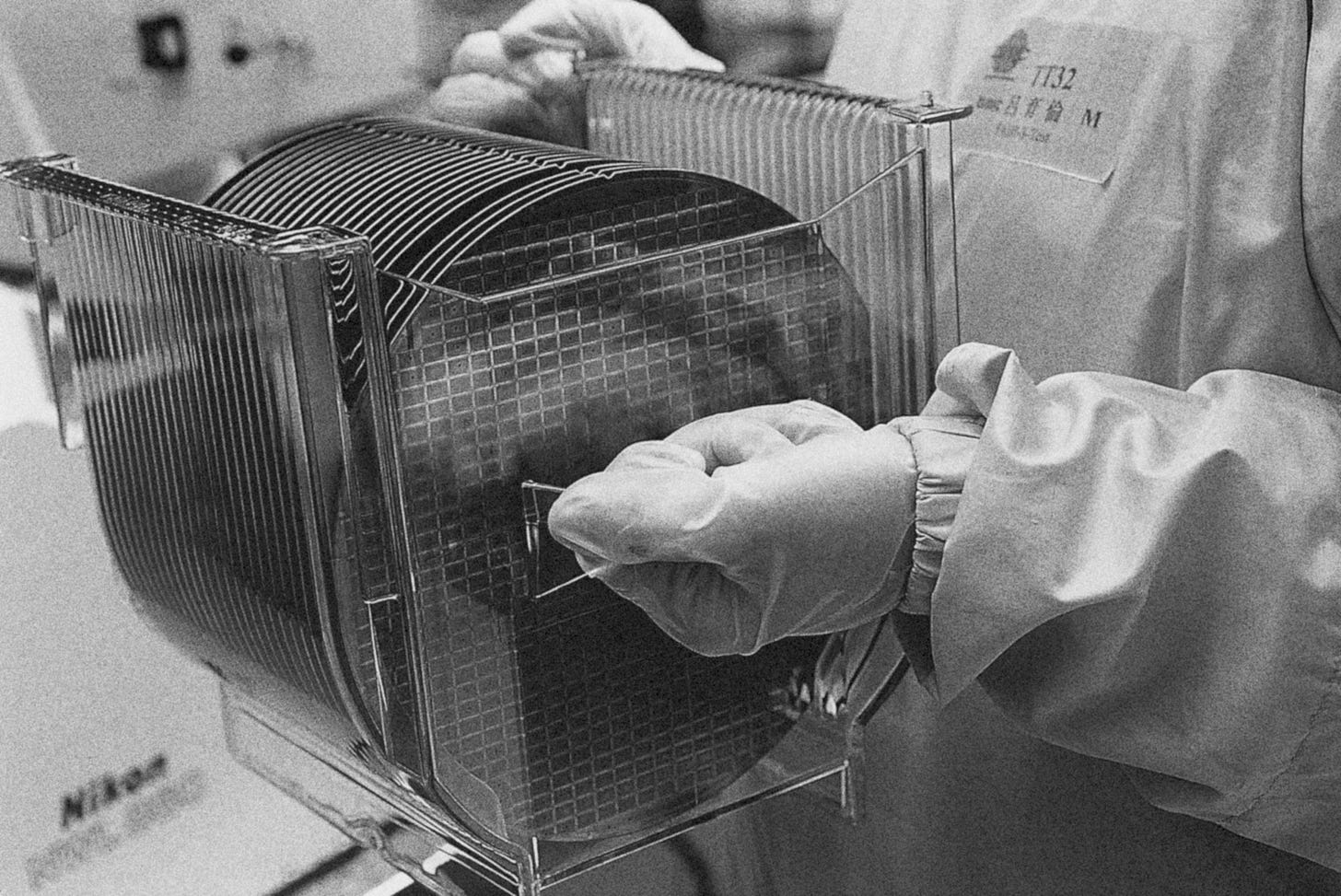

The business

TSMC sells two things:

Time-to-yield at the leading edge (manufacturing learning + process integration, delivered as a service).

A systems manufacturing for chip designers, increasingly including advanced packaging and related steps (“Foundry 2.0”).

TSMC itself frames the Foundry 2.0 scope as including all logic wafer manufacturing plus items like advanced packaging, testing, and mask making.

A central historical advantage is that TSMC is structurally non-conflicted versus customers: Morris Chang promised never to design chips, only to build them, and not compete with its customers. That neutrality helps customers share leading-edge designs and roadmaps, raising switching costs and deepening co-optimization.

Mapping the moat

How can TSMC’s business keep earning superior returns without being competed down?

Scale + learning curve (the experience curve becomes a barrier)

The economics of manufacturing push toward consolidation: the highest-volume manufacturer gains yield and spreads massive capital costs, reinforcing dominance. TSMC’s business is overwhelmingly leading edge: 4Q25 advanced-node mix (7nm and below) is at 77% of wafer revenue. 3nm alone is now large business (28% of wafer revenue in 4Q25). The system, from yield learning, equipment integration, defect density mastery, to customer enablement compounds with volume.

Ecosystem lock-in (Grand Alliance / platform effects)

Chip War describes TSMC as a “neutral player around which other companies design their products” coordinating a “Grand Alliance” of IP, equipment, and ecosystem partners where compatibility with TSMC’s processes becomes crucial.

Leading-edge customer commitments show up as NTOs/tapeouts and rapid node ramps. TSMC highlights N2 has received multiple NTOs, and positions N2P as a 2026 follow-on with stated PPA improvements.

TSMC’s moat increasingly resembles a high-frequency coordination problem solved better than competitors: designers, EDA/IP, packaging, materials, EUV, testing, and capacity planning all must move in sync.

Capital barrier that is getting higher, not lower

TSMC’s 2026 capex budget: US$52-56B. Capex allocation guidance: ~70-80% of advanced process, ~10% to specialty, ~10-20% to advanced packaging/testing/mask making. Even if a rival had the money, they need (a) the talent, (b) the supply chain, (c) the customer trust, and (d) the execution discipline, all at once, over multiple node cycles.

The financial engine: high returns and high reinvestment

From TSMC’s 4Q25 presentation (FY2025):

Revenue US$122.42B

Gross margin 59.9%, operating margin 50.8%

Capex NT$1,272B

Free cash flow NT$1,003B

Cash dividends NT$466.8B

Derived (from the same figures):

Capex ≈ 33.4% of revenue

FCF margin ≈ 26.3% of revenue

Dividends ≈ 46.6% of FCF

This a phenomenal operating franchise (margins + ROE), but it’s also a business where maintenance and growth capex are tightly intertwined. Will each capex wave preserve pricing power and share at the frontier?

TSMC’s management expects long-term ≥56% gross margin and high-20s ROE through the cycle. But they also explicitly flat gross-margin dilution from (1) early-stage overseas fabs and (2) initial ramp-up of 2nm, noting a 2-3 percentage point dilution in the early stage. TSMC is telling us that they’re building strategic redundancy and the next node, that it costs money, and that the franchise can absorb it and still clear the long-run hurdle.

Moving from smartphone cyclicals to AI compute infrastructure

The mix shift is the most under-appreciated change for anyone looking at TSMC like a 2016 smartphone supplier.

FY2025 revenue mix: HPC 58%, Smartphone 31%, IoT 6%, Automotive 5%. AI accelerators were a high-teens % of total revenue in 2025. Advanced packaging was slightly over 10% of 2025 revenue.

TSMC is increasingly exposed to (and enabling) the capex cycles of hyperscalers and AI platforms, besides consumer upgrade cycles. The platform is now wafer + package + system integration at scale.

Technology position: N2 in production, N2P/A16 next, packaging as a second bottleneck

TSMC states 2nm (N2) started volume production in 4Q25 and uses first-generation nanosheet transistors. TSMC’s 2022 disclosure framed N2 as delivering 10–15% speed improvement at same power, or 25–30% power reduction at same speed (vs N3), plus density gains. N2P is positioned as a 2026 performance-enhanced version, and notes N2 has received multiple NTOs.

Two disclosures matter here:

Revenue: advanced packaging >10% of 2025 revenue.

Capital allocation: advanced packaging/testing/mask making gets ~10–20% of 2026 capex.

Modeling TSMC as “wafer-only,” could lead to misreading both its TAM and its constraint. For AI systems, package-level bottlenecks can be as binding as wafer starts.

Geographic footprint: strategic resilience vs economic drag

The world’s dependence on Taiwanese chip production is a persistent strategic issue, and efforts to diversify manufacturing footprints are politically and economically motivated.

TSMC’s Arizona site:

Fab 21, Phase 1 (4nm): volume production began 4Q 2024.

Phase 2 (3nm): under construction, targeted for production in 2028.

Phase 3 (2nm/A16): planned, targeted by the end of the decade.

Management adds an important execution datapoint: yield and defect density in Arizona are “almost comparable” to Taiwan and the company is “working on speeding up” the schedule for the second fab.

Japan + Europe:

Japan fab started volume production in late 2024 with “very good yield,” and a second Japan fab construction started.

Germany (Dresden) specialty-tech fab is under construction, with ramp timing tied to customer needs.

First-order effect: Geographic redundancy reduces single-point geopolitical risk. Second-order: higher cost structure, early-stage inefficiencies, talent ramp, and a potential long-lived margin headwind (which TSMC quantifies as a 2–3ppt gross margin dilution early on).

How could TSMC fail? From existential to cyclical

Existential / discontinuity risks

Geopolitical disruption to Taiwan production and logistics.

Export-control regime shifts impacting customer mix and tool access (“chokepoints” as policy leverage).

Catastrophic infrastructure events (power/water/earthquake) that materially reduce output at the center of the network.

Moat erosion risks (slow killers)

Node execution slip (yield, defect density, cycle-time).

Packaging constraint persists: AI demand can be throttled by packaging scale and substrate availability, not just wafers.

Competitor breakthrough (Samsung or Intel Foundry) that matches both PPA and customer trust/ecosystem.

Economic/cycle risks (fast killers)

AI capex digestion → utilization drop → operating leverage reverses.

Overbuild risk: multi-year capex decisions made at peak demand can compress returns later. (TSMC itself is lifting capex materially into 2026.)

Customer concentration and bargaining power shifts (pricing pressure if customers have credible second sources).

Self-inflicted wounds (incentives/culture)

Talent dilution across multiple geographies; cultural mismatch can reduce the “2 a.m. fix” intensity that historically mattered in fabs. (Chip War discusses how operational intensity and equipment uptime discipline contributed historically.)

What must be true for TSMC to be a long-term compounding franchise from here?

Durable moat → durable owner earnings → intelligent reinvestment → shareholder returns.

As of today, the thesis would rest on the following:

TSMC remains the default frontier manufacturer (node leadership + yield). Advanced-node dominance in wafer mix; N2 already in volume production 4Q25; N2P roadmap.

AI/HPC demand stays structurally strong enough to absorb the rising capital base. HPC is 58% of revenue; AI accelerators high‑teens % in 2025; management’s 2024–2029 CAGR target.

Packaging scales with wafers (or else TSMC’s “system foundry” thesis under-delivers). Packaging already >10% of revenue; capex allocation explicitly includes packaging at 10–20%.

Overseas expansion doesn’t structurally reset margins below the long-run hurdle. Management quantifies near-term dilution (2–3ppt early), but reiterates long-term ≥56% gross margin and high‑20s ROE through-cycle.

The fat-tail geopolitical risk stays non-realized (or is sufficiently mitigated by diversification). TSMC is actively diversifying footprint, but Taiwan remains central.